# Self-Heating Effect in a 65nm MOSFET at Cryogenic Temperatures

Anton A. Artanov, Edmundo A. Gutiérrez-D. Alfonso R. Cabrera-Galicia, Andre Kruth, Carsten Degenhardt, Daniel Durini, Jairo Méndez-V, and Stefan van Waasen

Abstract—We characterized the thermal behavior of a 65 nm bulk-CMOS transistor, by measuring the self-heating effect (SHE) as a function of the bias condition. We demonstrated that at the base temperature of 6.5 K the channel temperature of the transistor can increase up to several tens of Kelvins due to power dissipation. The thermal behavior of the transistor is determined not only by the thermal response of the transistor itself, but also by the thermal properties of the surroundings, i.e., the source, drain, bulk and gate interfaces, the metal contacts and vias. On top of it, the thermal response is bias dependent through the bias dependence of power and self-heating. This information becomes relevant for the proper design of integrated circuits for quantum computing or other cryogenic applications, where the circuitry requires to be operated at a stable cryogenic temperature.

Index Terms—CMOS, Cryogenic temperature, Quantum Computing, Self-heating

#### I. Introduction

**▼**OMPLEMENTARY metal-oxide-semiconductor technology (CMOS) in cryogenic environments is a trending topic for the last decade. First low-temperature measurements of CMOS field-effect transistors (MOSFETs) were published in 1968 [1], [2], and interest in this topic has recently increased due to new cryogenic applications, such as outerspace devices, scientific instruments [3] and particularly quantum computing [4], [5]. The increasing number of qubits in quantum systems created the necessity of hardware, which is able to work in deep cryogenic temperatures. Along with several types of superconducting logic, CMOS integrated circuits seem to be a good candidate for this purpose, due to large experience in design and fabrication. Highly integrated system-on-chip solutions can be used as control and readout electronic systems for several types of qubits, providing the

This work was supported by Helmholtz Impuls- und Vernetzungsfond "Scalable solid state quantum computing" and Mexico-CONACyT.

A. A. Artanov, A. R. Cabrera-Galicia, A. Kruth, and C. Degenhardt are with Central Institute of Engineering, Electronics and Analytics, Electronic Systems, Forschungszentrum Jülich GmbH, Jülich, Germany (e-mail: a.artanov@fz-juelich.de).

E. A. Guttierez-D., D. Durini, and J. Mendez-V are with the Instituto Nacional de Astrofísica, Óptica y Electrónica (INAOE), Puebla, Mexico (e-mail: edmundo@inaoep.mx).

S. van Waasen is with the Central Institute of Engineering, Electronics and Analytics, Electronic Systems, Forschungszentrum Jülich GmbH, Jülich, Germany, and also with the Faculty of Engineering, Communication Systems, University of Duisburg-Essen, Duisburg, Germany (e-mail: s.van.waasen@fz-juelich.de).

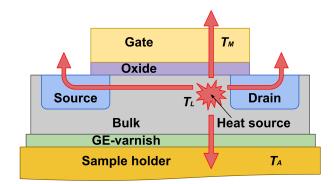

Fig. 1: The four thermal paths of the n-type transistor.

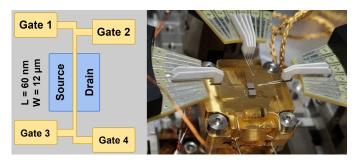

Fig. 2: Layout scheme of the measured sample (left) and a photo of the working area of the setup (right).

opportunity to scale up the number of qubits in quantum information processors [6]. Some of the design concepts even propose the placement of control electronics together with the qubit array on the same die [7].

However, as already reported by several authors [8]-[11], the presence of various scattering processes self-heats the transistor and makes its temperature different from that of the cryogenic environment, which should be accounted for the development of the proper cryogenic process design kit (PDK). Moreover, self-heating is not taken into account in most of the literature on cryogenic effects research in CMOS devices. The local heating influences the behavior of the device itself, as well as the behavior of other thermally connected devices. In case of quantum computing, electro-thermal effects in the CMOS could severely degrade the performance of the qubits or even render them unusable.

Therefore, understanding the way heat is generated in the active region of the transistor and how it diffuses away from the hot spot through the different thermal paths, becomes

Fig. 3: Measured gate resistance  $R_g$  at different ambient temperatures  $T_A$ , fitted with Fermi-like function (left Y axis) and gate resistance thermometer sensitivity (right Y axis).

essential for the design of high perfomance integrated circuits for cryogenic applications and the overall system design.

The purpose of our work is to investigate self-heating effect (SHE) in 65-nm bulk CMOS technology. With the use of the gate resistance thermometer technique, we have investigated thermal properties of the transistor and its surroundings. From the experimental data we also describe qualitatively the contribution of different thermal paths to the electro-thermal behavior of the transistor. A quantitative description would require the design of special test structure, with different geometries that allow for a quantitative thermal de-embedding.

# II. DEVICE TECHNOLOGY AND EXPERIMENTAL SETUP

Thermal behavior of a MOSFET is explained by the interplay of electrical and thermal parameters, such as Joule power P dissipated by the device, thermal resistance  $R_{th}$ and thermal capacitance  $C_{th}$ , surrounding the active region of the transistor. If we consider a static system where the transient thermal effects are neglected, then because of carrier scattering [12] in the active channel, most of the carrier energy is transferred to the lattice, which then translates into an increase of the local temperature  $T_L$  [13]. This is known as the self-heating effect [14]. As the Joule power is a function of the bias conditions, such as drain current  $I_d$ , gate voltage  $V_q$ , and drain voltage  $V_d$ , then  $T_L$  also becomes a function of the bias conditions. The thermal equilibrium of the transistor is reached when the cooling power, determined by temperature difference and thermal conductivity through the 4 different paths (as shown in Fig. 1), is equal to the self-heating power.

At this point, the differential temperature  $\Delta T$  is defined by the temperature drop across the four thermal paths:  $\Delta T = (T_L - T_A)$ . Therefore, a way to indirectly measure  $T_L$  is by setting a thermometer as close as possible to the hot spot in the active channel. For that purpose, in this experiment we design a gate resistor thermometer [15], configured as a 4-terminal device as shown in Fig. 2, left. The self-heating

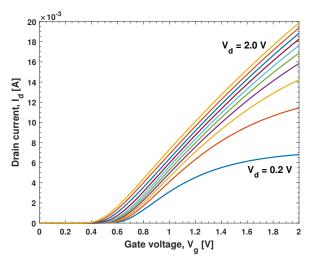

Fig. 4: Measured  $I_d$ – $V_g$  characteristics with  $V_d$  as a parameter at  $T_A$  = 6.5 K.  $V_d$  step size is 0.2 V.

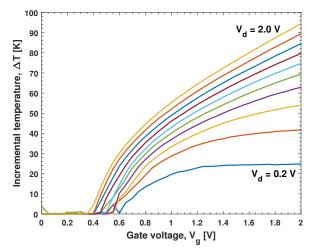

Fig. 5: Measured incremental temperature  $\Delta T$  versus  $V_g$  with  $V_d$  as a parameter at  $T_A$  = 6.5 K.  $V_d$  step size is 0.2 V.

structure was designed and fabricated in 65 nm CMOS technology by TSMC, with gate oxide thickness  $T_{ox}=1.9$  nm. The poly-silicon gate is used as a thermometer which is as close as possible to the source of heat produced in the active channel of the transistor. The selfheating test structure has  $(W/L)=12~\mu \text{m}$  / 60 nm geometry. As a matter of experimental demonstration we introduce results for a n-type 65 nm MOSFET, which can be later expanded for the p-type device.

The gate of the test transistor with its four contacts (Fig. 2, left) is used to calibrate the gate resistance as a function of the temperature, which is measured with the transistor in off mode. We used a closed-cycle cryostat attocube attoDRY800 with DC probing configuration (Fig. 2, right). The sample was glued to the sample holder with thermally conductive GE-varnish. The sample holder has a temperature sensor and a heater close to the sample area to control the holder's temperature. The Keysight B1500A Semiconductor Device Analyzer was used for all the DC measurements.

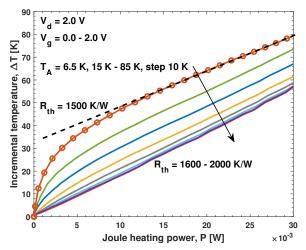

Fig. 6: Measured incremental temperature  $\Delta T$  versus Joule power P for  $V_d = 2.0$  V at several ambient temperature  $T_A$  values.

We performed a temperature-controlled measurement of the gate resistance dependence with respect to the base temperature (see Fig. 3). Using the four-terminal sensing technique, we apply a potential difference of 20 mV to the ends of the gate and measure the current. This approach provided a minor influence on the transistor behavior and negligible polysilicon gate self-heating, as the Joule heating power dissipation during resistance measurements is less than 400 nW. The measured data is fitted to a Fermi-like function (eq.1, [11]) in the 6.5 K - 95 K temperature range, as shown in Fig. 3.

## III. EXPERIMENTAL RESULTS AND ANALYSIS

The experimental data in Fig. 3 shows that the polysilicon resistance  $R_g$  is almost constant for temperatures below about 15 K, which is a result of residual impurity scattering, due to metallic behavior of polysilicon versus temperature [16]. As the resistance measurement accuracy in this range is 0.3 Ohm, data for channel temperatures lower than 15 K is not reliable. We set a time of 1 s before each measurement point in order to achieve thermal equilibrium over the whole chip. The  $I_d - V_g$  characteristics with  $V_d$  as a parameter are shown in Fig. 4.

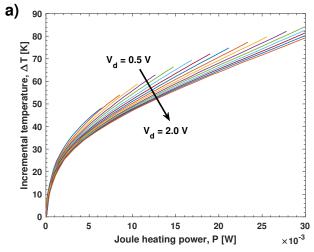

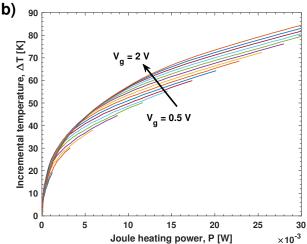

The transistor handles  $I_d$  up to 20 mA, which is equivalent to a heating power P of 40 mW, at  $V_g = V_d = 2.0 \ V$ . As seen from the Fig. 4 and 5,  $\Delta T$  is a function of  $I_d$ ,  $V_g$ , and  $V_d$ . For  $V_g = V_d = 2.0 \ V$  condition  $\Delta T$  raises up to 94 K. Plotting the incremental temperature  $\Delta T$  versus the Joule power ( $I_d$  times  $V_d$ ) gives a better perspective, as it is related to the thermal properties, like the thermal resistance  $R_{th}$  (Fig. 6, marked line).

The  $\Delta T-P$  curve for  $V_d=2.0~V$  with  $V_g$  sweeping from 0.0 to 2.0 V in Fig. 6 shows two regions: a nonlinear region for low Joule power magnitudes, and a linear region for high Joule power ones. Incremental temperature  $\Delta T$  is related to the Joule power through the thermal resistance  $R_{th}$  as described by equation:

$$\Delta T = R_{th} \cdot P \tag{1}$$

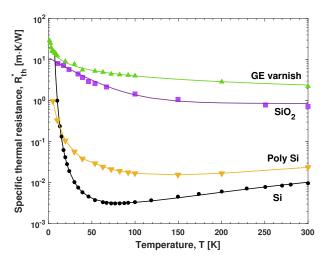

Fig. 7: Specific thermal resistance  $R_{th}^*$  versus temperature for different materials [17]–[22].

Fig. 7 allows for better understanding of the thermal performance, which is based on the temperature dependence of the thermal resistance. The data shown in Fig. 7 has been replotted and fitted from various references [17]–[22]. Because of the presence of SiO<sub>2</sub>, the heat flow sees a higher thermal resistance when flowing from the hot spot towards the SiO<sub>2</sub>. GE-varnish, which was used to glue the Si die to the cold plate, has higher thermal resistivity than Si, but large thermal contact area and small thickness of the varnish layer makes this path relatively high thermally conductive. The heat, generated at the active region of the channel, flows through the bulk and lateral paths of the drain and source, then through the vias and metal interconnects (Fig. 1). Under this thermal scenario, the thermal resistance of Si dominates the heat flow. In turn, any increase of temperature in the transistor will dramatically reduce the thermal resistance of Si by several orders of magnitude. The experimental data in Fig. 6 shows the temperature raise from the 6.5 K cold-plate value up to about 100 K. Thus, the Si specific thermal resistance  $R_{th}^*$  swings from about 30 m·K/W down to 0.004 m·K/W (Fig. 7). This enables heat flow from the transistor channel through the Si out through the source/drain contacts and varnish layer, leading to a thermalization of the

The profile of the  $R_{th}-T$  curve for Si, SiO<sub>2</sub>, and poly-Si (Fig. 7) is a function of doping profile and sample thickness [17], [20], [23]–[25]. Therefore, the magnitude varies according to thickness and doping or composition in the case of poly-Si and SiO<sub>2</sub>. In the case of Si, the minimum value  $R_{th}$  happens at about T=75 K and moves to a lower or higher temperature, depending on the doping concentration. The higher Si doping concentration, the higher the magnitude of the thermal resistance and the higher the temperature at which it reaches its minimum value or inflexion point [26].

In order to prove the Si thermal resistance domination over the other thermal components, the experiment was repeated for several higher temperatures, including  $T_A = 75$  K, which is the temperature at which  $R_{th}$  gets its minimum value and has an inflexion point. The incremental temperature  $\Delta T$  versus

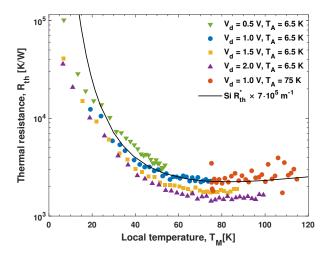

Fig. 8: Extracted thermal resistance  $R_{th}$  seen from the gate side as a function of the temperature  $T_M$  measured at the gate, for  $V_d$  of 0.5, 1.0, 1.5 and 2.0 V at  $T_A$  = 6.5 K and for  $V_d$  = 1.0 V at  $T_A$  = 75 K.

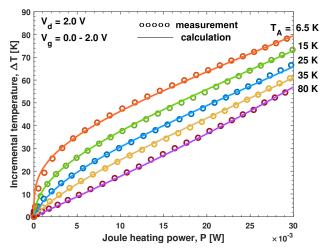

Fig. 9: Calculated and measured channel temperature increase as a function of the dissipated power for several  $T_A$ .

the Joule power for  $V_d=2.0~{\rm V}$  and  $V_g$  swept from 0.0 to 2.0 V is shown in Fig. 6. Starting from  $T_A=60~{\rm K}$  the  $\Delta T-P$  relationship is almost linear with a slight second-order polynomial behavior. The derivatives  $(d\Delta T/dP)$  of lines for  $T_A$  higher then 60 K give a thermal resistance  $R_{th}$  of 1600-2000 K/W. This result indicates that  $R_{th}$ , measured at the gate at temperatures close to 75 K, changes slightly, which is consistent with Fig. 7. Because of the increased thermal resistance of silicon, the SHE effect is more pronounced at  $T_A$  lower then 60 K, remaining almost constant as the  $T_A$  rises.

The plot of the derivative  $(d\Delta T/dP)$  versus the measured temperature at the gate for both  $T_A=6.5$  K and 75 K, is shown in Fig. 8. The data at  $T_A=6.5$  K is given for  $V_g$  sweep and  $V_d$  equal 0.5, 1.0, 1.5 and 2.0 V; the data at  $T_A=75$  K is given for  $V_d=1.0$ . Solid line is calculated from

the specific thermal resistance  $R_{th}^{*}$  curve for Si (Fig. 7), with the assumption that effective length versus effective area ratio is  $7 \cdot 10^5$  m<sup>-1</sup>. The  $R_{th}$  data, extracted at 6.5 K, nicely fits with that of 75 K, giving continuity to the  $R_{th}$  curve. The thermal resistance curves, that are seen from the gate side, have the same shape as the thermal resistivity curve of Si. That confirms the hypothesis, that Si thermal resistance dominates over the other thermal components.

In addition to that, we performed the modeling of the  $\Delta T - P$  behavior, based on the approach, proposed in [11]:

$$\delta \Delta T = R_{th}(T_A + \Delta T) \cdot \delta P \tag{2}$$

$$P = \int_0^{\Delta T} \frac{\delta \Delta T'}{R_{th}(T_A + \Delta T')} \tag{3}$$

Silicon specific resistance dependence over temperature multiplied by effective length versus area ratio, that serves as a fitting parameter, was taken as  $R_{th}(T)$  function in (3). The result is shown in Fig. 9. The measured and calculated data agree with each other, and that additionally confirms our analysis above.

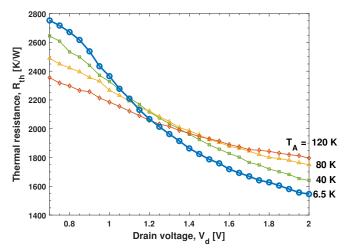

Thermal resistance, extracted at the gate side, shows noticeable dependence on bias voltages. As  $V_d$  increases from 0.5 to 2.0 V the  $R_{th}-T$  curve shows a reduction in magnitude. It is especially clearly visible in the Fig. 10. The dependence on bias voltages most likely is a result of the influence of bias voltages on thermal embedding resistance of the transistor. Linear parts of the curves are parallel to each other in Fig. 10 (b) and have decreasing slope in Fig. 10 (a). That means, that  $V_d$  increase causes the decrease of thermal resistance. The dependence of the thermal resistance  $R_{th}$  on the linear parts of the curves in Fig. 10 (a) on  $V_{ds}$  for several  $T_A$  is shown in the Fig. 11. The slope of this dependency decreases with temperature. However, the reason of this thermal resistance decrease remains unclear and will be a subject of further studies.

## IV. CONCLUSION

We introduced experimental results from a selfheating structure, fabricated using a commercial 65 nm TSMC CMOS technology. In this case the measurements were taken from a Si die attached with varnish glue to the cold plate of the cryostat. We have considered the four thermal paths determined by the bulk, source, drain, and gate (the passive thermal component). Due to the incorporation of different materials, such as the Si by itself with different doping levels, the SiO<sub>2</sub> and its interfaces with the channel and the gate, the polysilicon gate, the source and drain contact interfaces, and the glue used to attach the die to the cold plate, the thermal resistance is quite complex. The level of complexity increases when the local temperature actively changes with the bias condition. In highly integrated circuits, in turn, the nearby transistors will thermally interact with each other, changing each other's electrical behavior. This influence will be quite difficult to predict due to frequent change of dissipated power by each device.

Fig. 10: The dependence of  $\Delta T$  on Joule heating power P.  $V_g$  primary sweep and 0.1 V step  $V_d$  secondary sweep (a) and  $V_d$  primary sweep and 0.1 V step  $V_g$  secondary sweep (b).

All this his prompts for the development of a thermal-deembedding technique that enables the creation of dynamic or active thermal models for the CMOS technologies. These electro-thermal models should serve the purpose to reduce the thermal load, either by modifying the technology for specific cryogenic applications, such as bulk thinning or metal pillars in the bulk as heat exchangers, among other alternative approaches. Having a bias- and technology-dependent electrothermal model should serve for the proper design of integrated circuits for cryogenic applications.

#### REFERENCES

- [1] R. R. Green, "MOSFET operation at 4.2 K," Rev. Sci. Instrum., vol. 39, no. 10, pp. 1495–1497, May 1968, DOI: 10.1063/1.1683144.

- [2] C. G. Rogers, "MOST's at cryogenic temperatures," Solid-State Electron., vol. 11, no. 11, pp. 1079–1091, Nov. 1968.

- [3] E. A. Gutiérrez-D., M. Jamal Deen, and C. Claeys, "Silicon Devices and Circuits," in *Low temperature electronics, physics, devices, circuits, and applications*, New York, NY, USA: Academic Press, Oct. 2000, ch.2, pp. 105–257, ISBN: 9780080510507.

- [4] C. G. Almudever, L. Lao, X. Fu, N. Khammassi, I. Ashraf, D. Iorga, S. Varsamopoulos, C. Eichler, A. Wallraff, L. Geck, A. Kruth, J. Knoch, H. Bluhm, and K. Bertels, "The engineering challenges in quantum

Fig. 11: Dependence of thermal resistance  $R_{th}$  (linear regime), seen from the gate side, on drain-source voltage  $V_d$  for several ambient temperatures  $T_A$ .

- computing," in *DATE*, Lausanne, Switzerland, March 2017, pp. 836–845, DOI: 10.23919/DATE.2017.7927104.

- [5] B. Patra, R. M. Incandela, J. P. G. van Dijk, H. A. R. Homulle, L. Song, M. Shahmohammadi, R. B. Staszewski, A. Vladimirescu, M. Babaie, F. Sebastiano, and E. Charbon, "Cryo-CMOS Circuits and Systems for Quantum Computing Applications," *IEEE J. Solid-State Circuits*, vol. 53, no. 1, pp. 309–321, Jan. 2018, DOI: 10.1109/JSSC.2017.2737549.

- [6] C. Degenhardt, A. Artanov, L. Geck, C. Grewing, A. Kruth, D. Nielinger, P. Vliex, A. Zambanini, and S. van Waasen, "Systems Engineering of Cryogenic CMOS Electronics for Scalable Quantum Computers," in *IEEE ISCAS*, Sapporo, Japan, May 2019, pp. 1–5., DOI: 10.1109/IS-CAS.2019.8702442.

- [7] J. M. Boter, J. P. Dehollain, J. P. G. van Dijk, T. Hensgens, R. Versluis, J. S. Clarke, M. Veldhorst, F. Sebastiano, and L. M. K. Vandersypen, "A sparse spin qubit array with integrated control electronics," in *IEEE IEDM*, San Francisco, CA, USA, Dec. 2019, pp. 31.4.1–31.4.4, DOI: 10.1109/IEDM19573.2019.8993570.

- [8] E. A. Gutierrez-D., L. Deferm, and G. Declerck, "Experimental determination of self-heating in submicrometer MOS transistors operated in a liquid-helium ambient," *IEEE Electron Device Lett.*, vol. 14, no. 3, pp. 152–154, March 1993, DOI: 10.1109/55.215141.

- [9] B. M. Tenbroek, M. S. L. Lee, W. Redman-White, J. T. Bun-yan, and M. J. Uren, "Self-heating effects in SOI MOSFETs and their measurement by small signal conductance techniques," *IEEE Trans. Electron Devices*, vol. 43, no. 12, pp. 2240–2248, Dec. 1993, DOI: 10.1109/16.544417.

- [10] K. Raleva, D. Vasileska, A. Hossain, S.-K. Yoo, and S. M. Goodnick, "Study of self-heating effects in SOI and conventional MOSFETs with electro-thermal particle-based device simulator," *J. Comput. Electron.*, vol. 11, pp. 106–117, Jan. 2012, DOI: 10.1007/s10825-012-0384-0.

- [11] K. Triantopoulos, M. Cassé, S. Barraud, S. Haendler, E. Vincent, M. Vinet, F. Gaillard, and G. Ghibaudo, "Self-Heating Effect in FDSOI Transistors Down to Cryogenic Operation at 4.2 K," *IEEE Trans. Electron Devices*, vol. 66, no. 8, pp. 3498–3505, Jan. 2019, DOI: 10.1109/TED.2019.2919924.

- [12] L. Wang, W. Peng, J. Zhang, Y. Fang, and Y. Jiang, "Investigation of scattering mechanisms for scaled mosfets," in *IEEE ICSICT*, Guilin, China, Oct. 2014, pp. 1–3, DOI: 10.1109/ICSICT.2014.7021279.

- [13] R. Kibushi, T. Hatakeyama, K. Yuki, N. Unno, and M. Ishizuka, "Comparison of hot spot temperature between Si and SiC power MOSFET using electro-thermal analysis," in *IEEE ITherm*, Orlando, FL, USA, July 2017, pp. 921–925, DOI: 10.1109/ITHERM.2017.7992584.

- [14] F. J. De la Hidalga, M. J. Deen, and E. A. Gutierrez, "Theoretical and experimental characterization of self-heating in silicon integrated devices operating at low temperatures," *IEEE Trans. Electron Devices*, vol. 47, no. 5, pp. 1098–1106, May 2000, DOI: 10.1109/16.841246.

- [15] P. G. Mautry, and J. Trager, "Self-heating and temperature measurement in sub-μm-MOSFETs," in *Proc. ESSDERC*, Berlin, Germany, Sep. 1989, pp. 675–678, DOI: 10.1007/978-3-642-52314-4\_141.

- [16] Z. Boekelheide, D. W. Cooke, E. Helgren, and F. Hellman, "Resonant impurity scattering and electron-phonon scattering in the electrical resistivity of Cr thin films," *Phys. Rev. B*, vol. 80, no. 13, pp. 134426, Oct. 2009, DOI: 10.1103/PhysRevB.80.134426.

- [17] A. D. McConnell, S. Uma and K. E. Goodson, "Thermal conductivity of doped polysilicon layers," *Journal of Microelectromechanical Systems*, vol. 10, no. 3, pp. 360–369, Sept. 2001, DOI: 10.1109/84.946782.

- [18] V. J. Johnson, "A Compendium of the Properties of Materials at Low Temperature (Phase 1), Part II: Properties of Solids," in Wadd Technical Report, pp. 60–56, National Bureau of Standards, Boulder, CO, USA 1960.

- [19] J. G. Hust, and A. B. Lankford, "Thermal conductivity of aluminum, copper, iron, and tungsten for temperatures from 1 K to the melting point," in *Wadd Technical Report*, National Bureau of Standards, Boulder, CO, USA 1984.

- [20] M. Asheghi, M. N. Touzelbaev, K. E. Goodson, Y. K. Leung, and S. S. Wong, "Temperature-Dependent Thermal Conductivity of Single-Crystal Silicon Layers in SOI Substrates," ASME J. Heat Transfer, vol.120(1), pp.30–36, Feb. 1998, DOI: 10.1115/1.2830059.

- [21] D. de Faoite, D. J. Browne, F. R. Chang-Díaz, and K. T. Stanton, "A review of the processing, composition, and temperature-dependent mechanical and thermal properties of dielectric technical ceramics," *J. Mater. Sc.*, vol. 47, pp.4211—4235, May 2012, DOI: 10.1007/s10853-011-6140-1.

- [22] Temperature Measurement and Control Catalog, Lake Shore Cryotronics, Inc., Westerville, OH, USA, 2016.

- [23] J. Jaramillo-Fernandez, J. Ordonez-Miranda, W. Kassem, E. Oilier, and S. Volz, "Thermal conductivity of polycrystalline aluminum nitride films: Effects of the microstructure, interfacial thermal resistance and local oxidation", in *THERMINIC*, pp. 1–6, 2015, DOI: 10.1109/THER-MINIC.2015.7389602.

- [24] A. M. Darwish, A. J. Bayba, and H. A. Hung, "Accurate Determination of Thermal Resistance of FETs," *IEEE Trans. On Microwave Theory and Techniques*, vol. 53, no. 1, pp. 306–313, Jan. 2005, DOI: 10.1109/TMTT.2004.839916.

- [25] P. E. Hopkins, and L. M. Phinney, "Thermal conductivity measurements on polycrystalline silicon microbridges using the  $3\omega$  technique", *Journal of Heat Transfer*, vol. 131, pp. 043201-8, April 2009, DOI: 10.1115/1.3072907.

- [26] S. Kasap, J. Málek, and R. Svoboda, "Thermal Properties and Thermal Analysis: Fundamentals, Experimental Techniques and Applications" in *Springer Handbook of Electronic and Photonic Materials*, Cham, Switzerland:Springer, Cham, Oct. 2017, ch.19, DOI: 10.1007/978-3-319-48933-9\_19.